Non-Volatile Processors (NVPs)

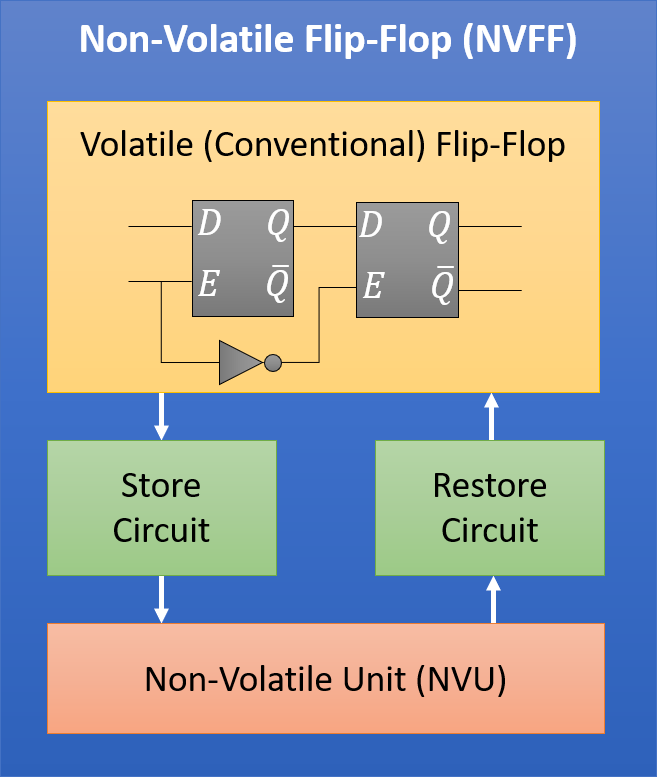

Emerging non-volatile memory technologies like ReRAM, STT-MRAM, and PCRAM, have led to the emergence of a new class of embedded processors, namely, Non-Volatile Processors (NVPs). In a NVP, the (conventional) registers are extended with non-volatility support using Non-Volatile Flip-Flops (NVFFs), e.g., Hypnos and Morpheus NVFFs in [1,2]. As a result, instead of depending on the conventional centralized and sequential non-volatile storage schemes (e.g. into a Flash memory), NVPs use a distributed and parallel storage scheme in which the contents of registers can be stored immediately in-place. This characteristic enables two highly sought features for embedded applications: the capability of working despite intermittent power supply and zero-leakage idle mode in battery-powered systems. Thanks to their in-place non-volatile storage capability, NVPs can incorporate fast and energy-efficient hibernation mechanisms for checkpointing the system state of the processor, see [2] as an example.

NVPs fundamentally depend on the emerging non-volatile memory technologies like ReRAM, STT-MRAM, and PCRAM to achieve in-place non-volatile storage. These technologies come with a series of shortcomings, e.g., variability [3] and degradation, which root in their physical and material characteristics and are unlikely to be remedied in near future or even at all. So, to meet the lifetime (longevity) requirements of the system as well as to provide excellent hibernation characteristics, e.g., energy efficiency and speed, the design of NVPs needs to effectively cope with the major challenges and shortcomings of the underlying memory technology. The conventional methods used in the design of memory chips cannot address these challenges because of the distributed deployment of memory cells in the NVPs. Therefore, these shortcomings must be taken into consideration and addressed in the design of NVFFs (see [1,2]) or the non-volatile units they incorporate (see [4,5]). Also being a new class of processors with new features and functionalities such as hibernation, novel tools, evaluation metrics, and methodologies are required for the design of NVPs based on NVFFs. This project investigates the challenges and opportunities in the design of NVPs, covering major parts of the design stack ranging from the device and circuit levels to architecture and system levels.

[1] Biglari, Mehrdad, Tobias Lieske, and Dietmar Fey. "High-endurance bipolar ReRAM-based non-volatile flip-flops with run-time tunable resistive states." Proceedings of the 14th IEEE/ACM International Symposium on Nanoscale Architectures (NANOARCH). 2018. [2] Biglari, Mehrdad, Tobias Lieske, and Dietmar Fey. "Reducing Hibernation Energy and Degradation in Bipolar ReRAM-Based Non-Volatile Processors." IEEE Transactions on Nanotechnology 18 (2019): 657-669. [3] Reuben, John, Mehrdad Biglari, and Dietmar Fey. "Incorporating Variability of Resistive RAM in Circuit Simulations Using the Stanford–PKU Model." IEEE Transactions on Nanotechnology 19 (2020): 508-518. [4] Biglari, Mehrdad, and Dietmar Fey. "Memristive voltage divider: a bipolar ReRAM-based unit for non-volatile flip-flops." Proceedings of the International Symposium on Memory Systems (MEMSYS). 2017. [5] Lieske, Tobias, Mehrdad Biglari, and Dietmar Fey. "Multi-level memristive voltage divider: Programming scheme trade-offs." Proceedings of the International Symposium on Memory Systems. 2018.