** NOVACore µ Architecture **

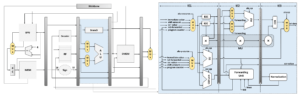

NOVA is a 7-stage in-order single-core RISC-V processor that supports RV32IZmmul_Zicsr ISA extension. It employs a synthesizable µ-architectural design method based on Canonical Signed Digit (CSD) representation to boost the computation power of a processor experiencing computation bottlenecks. Furthermore, the design integrates an extended seven-stage pipeline architecture, featuring a three-step execution stage (IE: IE1, IE2, IE3) that distributes the multiplication unit among them to optimize throughput and execution time. By introducing this three-step pipelined architecture to the execution units, the approach increases the throughput and operating frequency and enables up to 3-way loop unrolling, which is especially advantageous in applications with consecutive arithmetic computations, eg Matrix Multiplication. The attached picture represents the internal architecture of NOVA. when compared to the original design, Experimental data indicates a 2.37X improvement in operating frequency (from 114 MHz in the original design to 270 MHz in NOVA Core), leading to a 2.33X reduction in execution time and a 2.35X increase in throughput compared to the original open-source RISC-V processor on FPGA.

** NOVACore Demo Video **